Veröffentlicht am: 11.02.2018

Aktualisiert am: 31.03.2018

Von: JLusiardi

In Kategorie: Hardware

Um mal wieder über den berühmten Tellerrand zu blicken will ich mich mal mit etwas neuem beschäftigen. Die Wahl fiel auf FPGAs. Während des Studiums habe ich mich leider durch Wahl eines alternativen Praktikums um eine erste Erfahrung gebracht.

Für einen ersten Einstieg benötigt man nur Software, keine Hardware. Die Software (zumindest von Intel/Altera kann man gratis herunterladen. Dazu unten mehr. Da ich das am Anfang nicht wusste, habe ich über Amazon die im Folgenden genannten Produkte erworben.

Einkauf

- Altera USB Blaster (ein Klon), oder bei Reichelt im Original dient zum Programmieren über JTAG

- Altera FPGA Cyclone II Basisboard mit EP2C5T144C8, JTAG Anschluss, 3 LEDs und 1 Taster

Gesamtkosten: keine 30€, da der Klon deutlich günstiger als das Original mit fast 400€ ist.

Erste Erfahrungen

Zunächst sollen einige wichtige Erkenntnisse aufgeführt werden. Zu den beiden genannten Softwarepaketen:

- Der Cyclone II wird bis maximal Quartus II Web Edition 13.0sp1 unterstützt. Diese kann kostenlos mit einem myAltera-Account heruntergeladen werden (4.8GB). Nach der Installation sind es ca. 16 GB, wobei man hier beim Installationsumfang sicher sparen kann. Neuere Versionen unterstützen nur neuere FPGAs. Gestartet wird das Programm auf 64-bit Systemen über ./bin/quartus --64bit aus dem Installationsverzeichnis.

-

JTAG einrichten: unter Ubuntu 17.10 benötigt man zusätzliche udev-Regeln (Datei /etc/udev/rules.d/usbblaster.rules):

SUBSYSTEM=="usb",ATTR{idVendor}=="09fb",ATTR{idProduct}=="6001",MODE="0666" SUBSYSTEM=="usb",ATTR{idVendor}=="09fb",ATTR{idProduct}=="6002",MODE="0666" SUBSYSTEM=="usb",ATTR{idVendor}=="09fb",ATTR{idProduct}=="6003",MODE="0666" SUBSYSTEM=="usb",ATTR{idVendor}=="09fb",ATTR{idProduct}=="6010",MODE="0666" SUBSYSTEM=="usb",ATTR{idVendor}=="09fb",ATTR{idProduct}=="6810",MODE="0666"Diese ermöglichen den Zugriff auf für nicht root Nutzer. Anschließend kopiert man die Board-Descriptions nach /etc/jtagd:

cp $INSTALLDIR/linux64/pgm_parts.txt /etc/jtagd/jtagd.pgm_partsWeitere Informationen findet man unter bitsnbites.eu.

-

Mit ModelSim-Intel FPGA Edition 10.5c kann man auch im myAltera-Account herunterladen (3.1GB). Nach der Installation sind es ca. 7 GB. Vor dem Starten wird noch die Bibliothek freetype in Version 2.4.12 benötigt. Hinweise zur Installation liefert das Armadeus Project Wiki und ein Blog. Gestartet wird anschließend mit ./bin/vsim aus dem Installationsverzeichnis.

Spezifisch zu dem Basisboard gibt es noch folgendes zu sagen:

- Das Basisboard muss mit 5V über den entsprechenden Anschluss versorgt werden, sonst wird es nicht über den USB Blaster beim JTAG Scan erkannt. Hierbei liegen die 5V innen an! Es handelt sich um einen 2.1mm/5.5mm Hohlstecker. Update: Die Stromversorgung ist auch über P8 möglich, hier ist der 5V Pin weiter in Richtung Platinenmitte und GND Richtung Rand platziert.

-

Wichtige Pins sind wie folgt belegt:

Pin-Nummer Pin-Funktion Pin 3 D2 (LED, Output) Pin 7 D4 (LED, Output) Pin 9 D5 (LED, Output) Pin 17 CLK (50 MHz, Input) Pin 144 Taster (Input) Pin 73 10uF nach GND, 10K an Vcc Pin 26 an 1.2V VCC angeschlossen Pin 27 an GND angeschlossen Pin 80 an GND angeschlossen Pin 81 an 1.2V VCC angeschlossen Hier ist beim Anschluss von an weiterer Hardware entsprechend Vorsicht geboten.

-

Der Schaltplan des Basisboards befindet sich u.a. hier:

Schaltplan des Basisboards (Quelle: http://artofcircuits.com)

Erstes Projekt

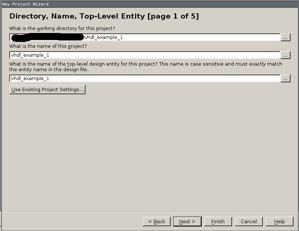

Wir starten Quartus II und wählen den "New Project Wizard". Zunächst wird das Projekt benannt:

Erster Schritt des Wizards

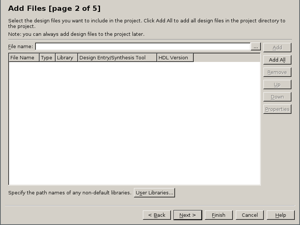

Anschließend kann man bereits existierende Dateien hinzufügen (wir haben allerdings noch keine):

Schritt 2 des Wizards

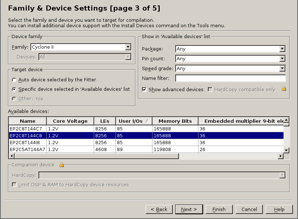

Die Auswahl des FPGAs (hier die Selektion für den FPGA auf dem Basisboard):

Schritt 3 des Wizards

Einige Informationen über den vorhandenen FPGA werden hier auch aufgezählt:

- 8256 LEs (Logic Elements) sind die Basisbausteine, im Detail beschrieben auf Seite 2-2 im Cyclone II Architecture Dokument. Jeweils 16 davon werden zu einem LAB (logic array block) zusammengefasst (516 sind vorhanden).

- 85 User I/Os (Ein/Ausgänge, die für den Entwickler verfügbar sind)

- 165888 Bit Speicher in 36 M4K Blöcken

- 36 9x9-Bit Mulitplizierwerke oder alternativ 18 18x18 Multiplizierwerke

- 2 PLLs

- 8 globale Takte

Nun hat man ein leere Projekt erzeugt. Mit "File" und "New" erstellt man eine neue VHDL Datei.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity vhdl_example_1 is

port(

clk: in std_logic;

led: out std_logic

);

end vhdl_example_1;

architecture bhv of vhdl_example_1 is

signal count: integer := 1;

signal tmp: std_logic := '0';

begin

process(clk) begin

if(clk'event and clk = '1') then

count <= count + 1;

if (count = 25000000 ) then

tmp <= NOT tmp;

count <= 1;

end if;

end if;

led <= tmp;

end process;

end bhv;

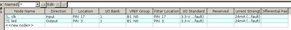

Diese speichert man unter dem Namen vhdl_example_1.vhd ab. Mit Processing und Start Compilation kann man das Übersetzen starten. Unter Assigments und Pin Planner starten wir die Zuordnung der unter Port definierten Ein-/Ausgänge. Folgende Zuordnung muss vorgenommen werden:

- clk auf Location PIN 17

- led auf Location PIN 3

Ausschnitt der konfigurierten Pins

Als letzten Schritt muss der FPGA noch ueber den JTAG Anschluss programmiert werden. Dazu verwendet man den unter Tools den Programmer. Zunächst wählt man unter Hardware Setup den USB-Blaster aus. Als Datei fügt man output_files/vhdl_example_1.sof hinzu und als Device den FPGA des Basisboards. Anschließend kann man mit Start die Programmierung starten.

Einstellungen im Programmer

Sollte dies nicht (mehr) funktionieren, kann es helfen den USB-Blaster kurz vom USB zu trennen.

Hat alles funktioniert, sollte die LED D2 mit 1Hz blinken:

Update 2. März 2018 zum Thema alternative Stromversorgung.

Update 31. März 2018 zum Thema JTAG einrichten

Update 20. Dezember 2019 Genauen Chip-Typ korrigiert